计算机网络从20世纪60年代出现至今已经过了整整半个世纪,其使用目的从军事、科研转变为娱乐、商务,应用从简单的邮件、BBS发展到搜索、即时消息、Web2.0、P2P、电子支付等等,参与网络的终端与网民的数量快速增长,这些变化促使网络信息高速公路不断以增加带宽容量来满足发展的需要。特别是进入21世纪后,云计算、三网融合、移动互联网、物联网等新兴技术再一次推动了网络的飞速发展。根据中国互联网信息中心(CNNIC)发布的***数据显示,截止到2010年6月底我国网民已经达到4.2亿,其中手机网民更超过了2.77亿,中国互联网国际出口带宽达到了100万Mbps。在如今的网络建设中,10G的网络数据流量已经屡见不鲜,而根据“吉尔德定律”,主干网带宽还将继续增加。

面对如此复杂的应用和庞大的用户群体,如何解决高速网络流量环境下的信息安全问题,特别是应用层安全,成为众多信息安全企业亟待解决的问题。其实,自从信息安全产业诞生以来,对CPU高处理能力的需求就没有停止过。为了获得更高的处理性能,众多企业也进行了很多尝试。纵观CPU技术的发展历史可以简单分为两种方案:

◆提高单兵作战的能力

在多核CPU出现之前,无论是不断提高主频,还是从X86到FPGA、ASIC、NP架构的转变,其目的都是为了提高单颗CPU的处理能力。但由于散热量高、开发难度大、开发周期长等诸多原因,上述技术的发展都不同程度受到了制约,难以满足超高速流量下网络安全产品对处理性能的需求。

◆发挥协同作战的优势

一个人的力量毕竟是有限的。由于散热、时钟频率、制造工艺等原因,单颗CPU主频的提升逐渐放缓(4GHz已经接近当前制造工艺的极限),而FPGA、AISC、NP等技术方案在需求变化快、要求应用层处理能力强的信息安全领域也显得捉襟见肘。因此在寻求提高单颗CPU处理能力的同时,技术人员也一直没有停止过对MP(Multi-Procesor)多处理器的研究。

SMP(Symmetric Multi-Processing)对称处理结构是早期的一种方式,即在一块主板上汇集一组处理器(多CPU),各CPU之间共享内存子系统以及总线结构,例如:我们常说的双至强,也就是两路CPU,是对称处理器系统中最常见的一种。这种方式对主板和CPU的要求比较高,而且随着CPU数目的增多,需要占用更大的主板面积、会带来更大的功耗。

CMP(Chip Multiprocessors)即单芯片多处理器,也就是我们常说的多核。其核心思想是将大规模并行处理器中的SMP对称多处理器集成到同一芯片内,各个处理器并行执行不同的进程。由于CMP结构被划分成多个微处理器核来设计,每个核都比较简单,有利于优化设计,解决了主频提升带来的高温、高功耗的问题,但同时整个芯片提供了更高的处理性能,因此更有发展前途。

多核市场目前由两大阵营组成:Intel和AMD公司组成的X86阵营;NetLogic、Cavium、Telira、ARM、IBM等公司组成的MIPS阵型。X86阵型采用CISC(Complex Instruction Set Computing)复杂指令集,按顺序串行执行程序命令,控制简单,更适合PC及中、低端服务器使用。而MIPS阵营采用的是RISC(Reduced Instruction Set Computing)精简指令集,其相对于CISC指令来说格式统一,种类和寻找方式较少,并采用了“超标量和超流水线结构”,大大提高了处理速度,适用于网络通信、信息安全、高端服务器等领域。

为了进一步提升在信息安全领域的竞争力,MIPS架构阵营在多核心的基础上提出了一个新的概念SoC(System on Chip),即片上系统,将网络连接、负责均衡、加/解密、应用加速等功能集成在一个芯片上。MIPS多核架构的发展为开发适应超高速网络流量的网络安全产品提供了基础。

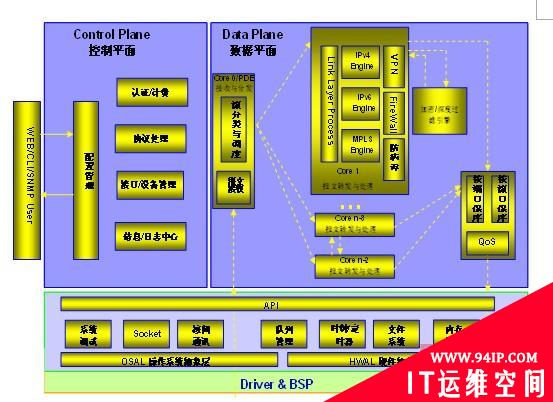

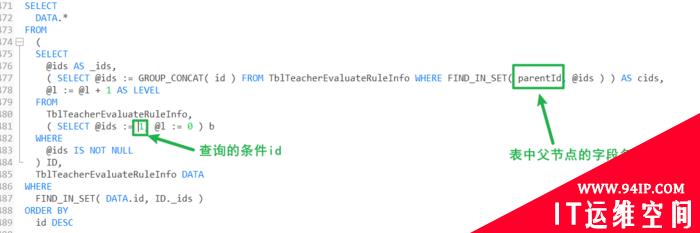

目前在多核CPU的使用上有两种思路:一种是Linux系统的SMP;还有一种是NP的控制与数据分离的思路。SMP方式开发简单、快捷,可以充分复用以前的软件,但很难做到智能地调度各个CPU上的资源。而网络安全产品对数据处理能力要求很高,不仅要求报文能够得到及时处理,还要求能够提供比较丰富的安全业务,如深度检测、报文过滤等,所以有必要把数据处理和业务处理分离,由单独的CPU并行处理,整个系统的性能将有很大的提升。联想网御VSP平台就是基于NP控制与数据分离的思想进行开发的。我们把软件系统,抽象成四个子系统:控制平面、数据平面、系统服务平面、驱动与BSP。

图1 VSP软件平台逻辑结构

为了充分调用多核心协同工作,联想网御提出了Windrunner矩阵式并行处理算法,对多CPU内核进行矩阵式管理。例如:联想网御的***端产品可以虚拟出多达64个vCPU:

图2 Windrunner矩阵式并行处理算法示意图

采用“8×8矩阵式并行处理系统”,将64颗vCPU排列为矩阵,从并行计算和流水线2个维度进行并行处理。所有的数据将被分配到8条流水线进行处理。每条流水线都具备8个环节,每个环节都有一个vCPU进行数据处理。“8×8矩阵式并行处理系统”不仅仅是多颗并行处理数据,还进一步引用流水线技术使得数据处理比原先更高效。Windrunner vCPU调度系统还会依据每条流水线上vCPU的工作饱和度情况实施调度,将较为空闲的vCPU调度到其他流水线中。

转载请注明:IT运维空间 » 安全防护 » 多核架构 高端网络安全产品的必由之路

发表评论